离开集成电路谈信息安全便是追求无源之水无根之木。为了保障应用于国计民生各个领域的电子信息系统的安全,我们必须从集成电路的硬件安全着手。

个人电脑的普及给半导体产业带来了早期的增长动力,之后移动通信设备的发展让人们将电子芯片携带在身边。伴随着近年来物联网技术的大潮,一片片以普通硅砂为原材料的芯片,很快就会像粒粒细沙一般遍布世界的每一个角落。

硬件安全芯片便是众多芯片中至关重要的一类。它们如同便衣保镖,默默保护着现代人生活的各个方面。硬件安全芯片在我们的生活中无处不在,从提供互联网购物和金融服务的运算中心到目前正在逐步取代现金的移动支付;从遍布在城市各个角落的移动通信基站到公共交通使用的一卡通;从基于芯片的银行卡和信用卡到医疗电子和个人健康器械,不胜枚举。可以说,硬件安全保障着国计民生的各个领域。

要保证一款芯片的安全,首先要确保整个产业链是可信和安全的。但是芯片是社会大分工的产物,需要遍布全球的成百上千家企业的参与和协作才能完成;所以需要通过技术手段并辅以行政手段来确保从最初的设计及验证,到之后的制造测试和封装,以及最后的物流和运输均是安全可控的。从这个角度来说,自主研制并不意味着安全。

现代信息安全系统为使用者提供了保密性、完整性验证和认证等密码功能和服务。提供这些服务的系统的稳定性、安全性和可靠性便成为了重中之重。对于设计者和工程师来说,设计和实现这样一个硬件安全系统是一项非常大的挑战。因为硬件安全系统往往需要同时满足传统的性能指标和额外的安全指标,而两类指标所指向的设计实现方向往往是相互矛盾的。

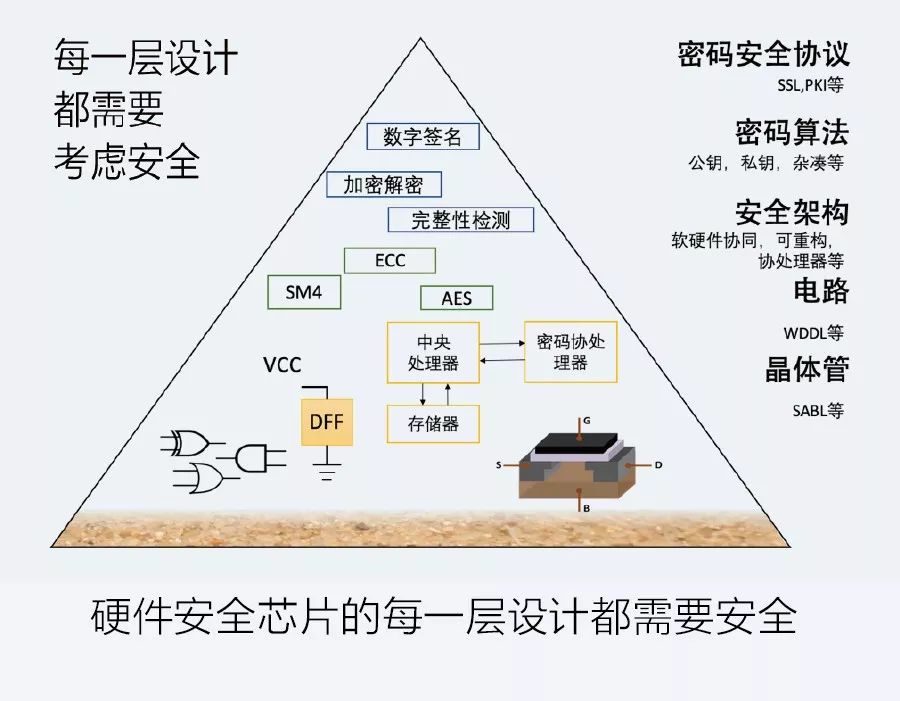

一般来说,安全计算设备的体系结构是分层的。每一层的安全都建立在对下面一层的信任上。系统的最底层通常由一种叫做信任根(root of trust)的模块组成。信任根是受到系统其他模块信赖的一组功能。纯粹的软件层面的安全解决方案并不存在,因为这一层面的安全解决方案一般都会被低于其的底层攻击所绕过。所以信任根的功能模块往往都是基于底层硬件实现的。由此可见,只追求系统安全而不考虑硬件安全无异于缘木求鱼。

设计硬件安全芯片需要参与到集成电路设计的每一个环节,包括从晶体管的设计到标准单元库的选用,从系统架构设计到密码算法实现再到最终协议的设计。一个系统的安全性取决于它最薄弱的一环。设计者需要考虑系统各个方面的安全, 而攻击者只需要攻击一点就好了。

所谓“道高一尺,魔高一丈”,集成电路的硬件安全研究是与攻击方法互相竞争发展的。早期针对安全系统的攻击主要集中在对相关密码算法的数学分析和破解上。近些年来涌现出众多新型的物理攻击方法,其中非常流行的两种物理攻击类别是旁路信息攻击和故障注入攻击。旁路信息攻击利用安全密码系统运行时的旁路信息来破解硬件系统安全,例如指令操作运行时间、系统瞬时功耗、电磁辐射和集成电路的光子释放信息。学术界和工业界也在持续研究各种抵抗旁路攻击的方法。故障注入攻击则是一种通过在电路运行过程中引入特定类型的错误,并分析故障传播而最终攻破密钥的攻击方法。相比于一般需要大量曲线采样的功耗攻击,故障攻击仅需少量错误密文即可实现。

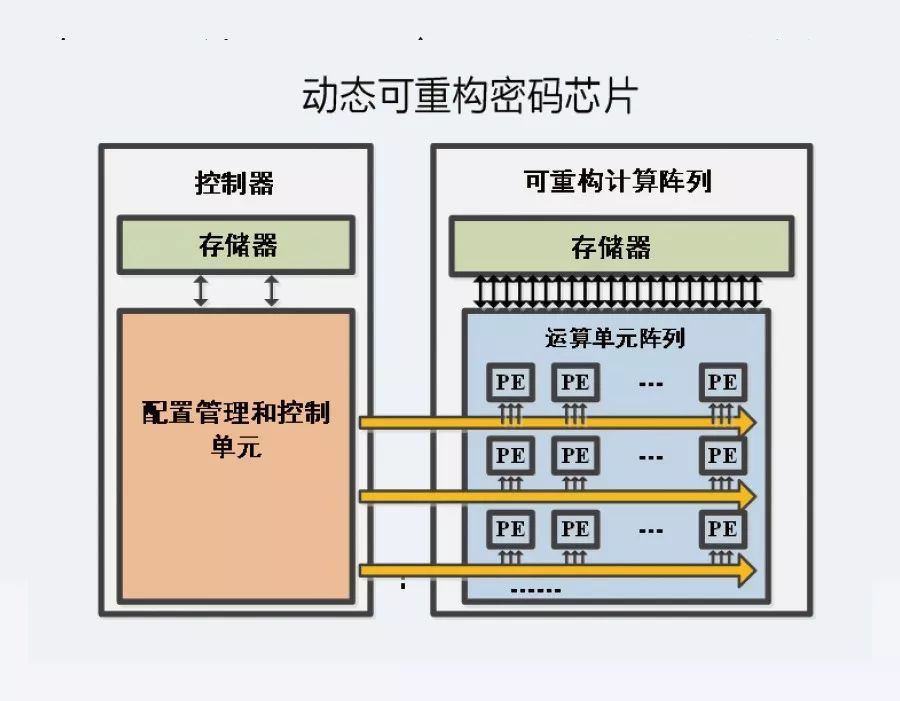

为了满足应用场景下的安全性、灵活性、高性能和低功耗应用需求,清华大学密码芯片与硬件安全研究团队提出了新型动态可重构密码芯片关键技术。其中抵御故障攻击的时域空域随机重构技术和抵御功耗攻击的冗余噪声随机重构技术服务于密码芯片安全性的要求。针对不同应用场景,研究团队研发了基于熵扩散混淆组件参数可配的可重构运算单元架构技术,激进、分支流水和令牌控制的密码任务并行化技术,以及密码数据流图引导的可重构配置信息管理技术,进而服务于密码芯片的高性能、高能效和灵活性需求;利用这3种技术,分别从计算、控制和配置3个方面给出了适合密码芯片应用的可重构芯片设计技术。此外,为了满足物联网设备的低功耗要求,研究团队还提出了密码计算强度感知的可重构阵列电压自适应技术。

除了物理攻击之外,硬件系统的安全还饱受各种漏洞的威胁。

2018年初,媒体披露主流高性能CPU普遍存在“熔断”和“幽灵”等多个严重影响信息安全的安全漏洞。本次漏洞事件除了影响范围广泛之外,和以往一个显著的区别是:它们都是硬件漏洞。目前的主要解决方案大部分都着眼于通过软件补丁减轻危害,即使通过硬件固件更新也仅仅能够修补部分漏洞。

在此次事件中,大部分的软件安全方案都束手无策,甚至无法提出有效的方案检测漏洞是否被利用。原因在于漏洞所依赖的硬件预测执行行为在软件层面完全不可见。

到目前为止,漏洞事件仍然持续发酵,随着研究的深入,不断有新的漏洞被发现;与此同时,如何兼顾性能和安全这一话题也开始在处理器架构、芯片设计领域的学术和工业界引发广泛的讨论和反思,可谓影响深远。

CPU芯片的硬件安全是计算系统的安全根基。无法确保CPU的硬件安全,就无法保证运行其上的软件的安全,与之紧密关联的系统安全和网络安全则更无从谈起。

针对该难题,研究团队提出了基于高安全、高灵活可重构架构的“CPU硬件安全动态检测管控技术”。这一技术克服了在CPU芯片商业部署前进行安全检测这种传统做法的先天不足,在CPU芯片部署后上电运行的过程中,用前文提到的新型动态可重构密码芯片关键技术对CPU的所有重要行为(包括指令执行、内部状态变化、与外部存储及网络设备的数据交互,以及预测执行、缓存控制在内的微架构行为等)进行快速采样和实时分析。无论硬件木马、漏洞、后门,还是恶意利用前门的行为,都能被及时发现并实施按需管控。

2018年7月,清华大学密码芯片与硬件安全研究团队和澜起科技采用上述技术研制了津逮高性能CPU芯片。这是全球首款采用第三方的硅模块来动态监控处理器内核硬件安全状况的CPU。联想、长城电脑、新华三集团等已完成了基于津逮CPU的高性能商用服务器的研制,并将于近日上市销售(型号分别为联想SR651、长城JW920、新华三R4900)。

该技术已成功入选第五届世界互联网大会(2018年11月)15项全球领先科技成果。这是国内高校原创技术成果第二次入选该会议全球领先科技成果(中国科学技术大学的光量子计算机曾于2017年入选)。

一劳永逸的硬件安全解决方案并不存在,新的攻击方法和安全威胁不断地涌现。立足当今,展望不久的未来,可以预见实用量子计算机的研制成功会摧毁现有公钥密码算法的数学根基;快速发展的人工智能技术被广泛用于包括旁路分析和故障注入等在内的攻击手段中;物联网设备的无处不在以及大数据时代的到来为保护个人隐私的技术提出了新的挑战。保障集成电路硬件安全任重而道远。

致谢:感谢国家自然科学基金面上项目“动态局部重构密码芯片抗物理攻击关键技术研究”(项目编号:61672317)的支持。

本文刊登于IEEE Spectrum中文版《科技纵览》2018年11月刊。

专家简介

刘雷波:清华大学教授。

杨博翰:清华大学博士后。

朱敏:清华大学无锡应用技术研究院高级工程师。

声明:本文来自悦智网,版权归作者所有。文章内容仅代表作者独立观点,不代表安全内参立场,转载目的在于传递更多信息。如有侵权,请联系 anquanneican@163.com。