长期以来,在量子计算领域,关于“Shor算法(用于破解现代加密体系的算法)”的资源估计一直是悬在行业头顶的达摩克利斯之剑。传统的资源估算认为,要破解RSA-2048加密系统,至少需要数百万个物理量子比特。这种“天文数字”量级的硬件需求,让很多人认为实用的容错量子计算(FTQC)仍需数十年之久。

然而,就在3月30日,由Madelyn Cain、Qian Xu、黄信元以及量子计算先驱John Preskill等人组成的研究团队在预印本平台arXiv上发表了一项重磅成果。通过融合高速率量子纠错码、高效逻辑指令集与电路设计的最新研究进展,研究团队证明:仅需10000个可重构原子量子比特,即可在密码学相关规模下运行Shor算法。

这表明,我们距离量子计算的“有用时刻”,可能比预想中近得多。

悬顶之剑

量子计算自诞生起,便以颠覆经典计算的潜力成为全球科技竞争的核心赛道,而Shor算法正是量子算力最具标志性的“杀手锏”。

1994年,数学家Peter Shor提出这一算法,证明量子计算机可在多项式时间内完成大整数质因数分解与离散对数求解,直接动摇RSA、ECC等全球通用公钥密码体系的安全根基,成为衡量量子计算实用价值的重要标尺。

理论的背后,是长期难以跨越的工程壁垒。Shor算法对量子硬件的核心要求有二:一是足够数量的逻辑量子比特,二是成熟的量子纠错机制。量子态极易受环境干扰产生错误,必须通过量子纠错,用数十至数百个物理量子比特编码1个稳定的逻辑量子比特,这使得算法的物理比特需求呈指数级增长。

过去,行业对密码相关规模Shor算法的资源估算始终停留在百万级物理比特的阶段。

早期研究显示,分解2048位RSA密钥需2000万个物理量子比特,即便经过多轮优化,表面码架构仍需100万个以上物理比特,运行时间以周为单位。而当前最先进的量子处理器,物理比特规模仅停留在千级,且未实现完整容错,巨大的资源鸿沟让Shor算法长期停留在“理论可行、工程无望”的困境。

在多种量子计算平台中,中性原子近年来表现突出。光镊阵列可实现原子量子比特的动态重构与非局域连接,长相干时间、高并行操控、易规模化的特性,完美适配量子纠错的高开销需求。2025-2026年,全球实验室相继实现6000+原子相干阵列、448原子容错计算,为大规模算法落地奠定硬件基础。

一边是密码安全的迫切需求,一边是硬件技术的蓄势待发,如何通过理论与架构创新,打破Shor算法的资源枷锁,成为量子计算领域的核心命题。

三重创新重构Shor算法资源模型

本研究通过高码率纠错码、高效逻辑架构、并行电路设计三重底层创新,实现了算法与硬件的深度协同,改写了Shor算法的资源需求曲线。

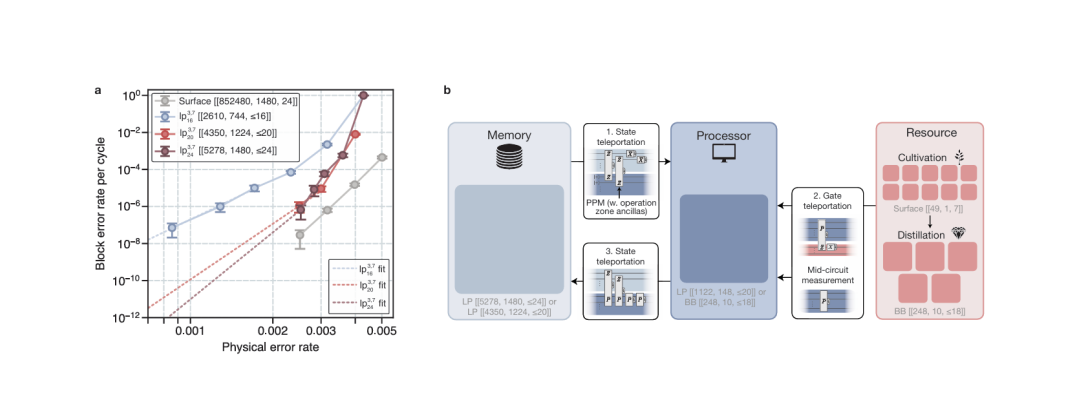

(一)高码率qLDPC码

量子纠错是容错计算的核心,传统表面码编码率仅4%左右,意味着96%的物理比特都用于纠错,资源利用率极低。研究团队创新性采用高码率量子低密度奇偶校验码(qLDPC),通过非局域连接设计,将编码率提升至30%,用更少物理比特实现更强的错误保护。

图:高速率量子纠错码性能与逻辑计算编译流程

研究团队特别优化了提升乘积(LP)码的家族,可在1个码块内编码1000+逻辑量子比特。数值模拟显示,在0.1%的物理错误率下,最大码距的码块每周期失败率低至10⁻¹¹——相当于每运行一亿次操作,预期错误不到一次。

这种高密度编码能力,直接将Shor算法的比特开销降低一个数量级,是实现万比特突破的重要基石。

(二)分区架构

研究团队设计了全新的中性原子分区容错架构,将量子计算机划分为四大功能区,实现计算、存储、纠错的专业化分工:

-存储区:用高码率LP码长期保存量子信息,负责数据缓存;

-处理区:采用小型专用码执行核心计算,兼顾速度与开销;

-操作区:辅助完成逻辑门测量,实现量子态读写与编辑;

-资源区:批量生成魔术态,实现通用量子计算。

该架构借鉴经典计算机“存算分离”思想,结合中性原子可重构特性,让每个区域各司其职,避免资源浪费。操作区仅占总量子比特的10%-20%,大幅提升整体算力效率,解决了传统架构“全量计算、全量纠错”的冗余问题。

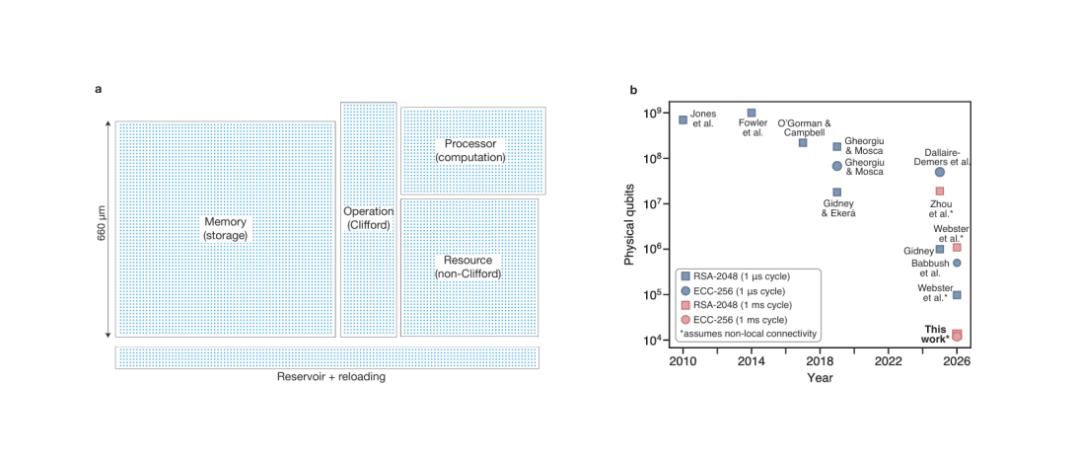

图:中性原子容错量子计算机架构与Shor算法物理量子比特需求演进

(三)并行编译

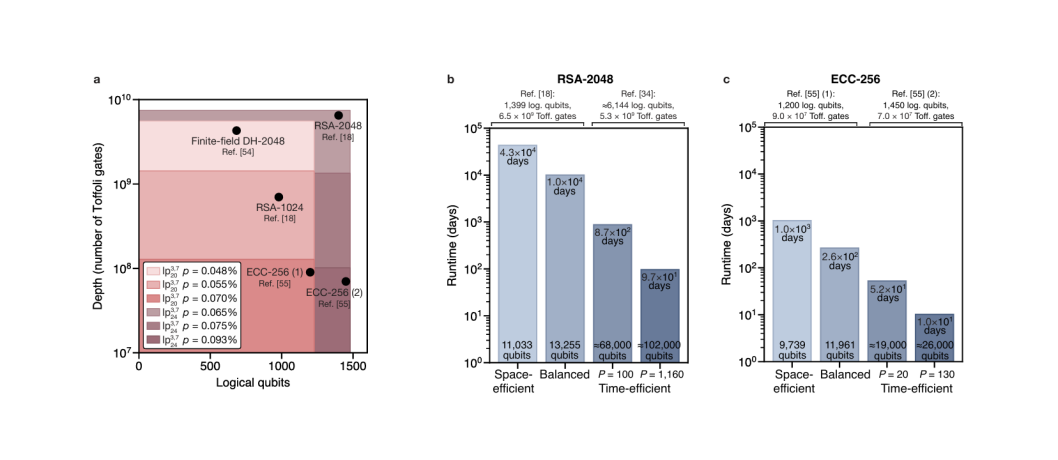

针对Shor算法电路深度大、门操作多的痛点,研究团队优化了逻辑编译方案,将算法拆解为可并行的子电路,通过并行逻辑操作与并行魔术态蒸馏,实现时间开销的指数级降低。

研究验证了三种架构方案,覆盖不同资源场景:

-空间高效型架构:约10000物理量子比特,最小化硬件需求,适合近近期落地;

-平衡型架构:约12000物理量子比特,平衡算力与开销,综合性能最优;

-时间高效型架构:约26000物理量子比特,最大化并行度,速度提升两个数量级。

通过按需配置的架构设计,研究团队实现了从万比特可行到万比特高效的跨越,使得Shor算法不再受限于极端硬件条件。

量子计算首次进入“可工程规模”

当前中性原子实验已实现三大关键突破:6100原子高相干阵列、448比特容错计算、低于纠错阈值的通用操作,与研究所需的10000比特规模仅一步之遥。研究团队通过激光功率优化、动态光束扫描等技术,可将高保真纠缠的原子数量提升3个数量级,完全满足万比特系统的硬件要求。

在现有实验进展基础上,研究团队以RSA-2048和ECC-256两大核心密码标准为测试基准,全面验证了本研究方案的实用性。

▶核心结论:仅需约10000个可重构原子量子比特即可在密码学相关规模上执行Shor算法。

▶时间效率:假设1ms稳定子测量周期,10000比特架构下破解ECC-256需数百天,11000-14000比特架构分解RSA-2048需数年。通过增加量子比特数量实现更高并行度,ECC-256运行时间可缩短至10天(约26000量子比特);RSA-2048可缩短至97天(约102000量子比特)。

▶资源节约:相比传统表面码架构(需约2000万量子比特),本研究将量子比特需求降低了三个数量级;相比近期基于小码块qLDPC的架构,仍实现了一个数量级的节约。

图:RSA-2048与ECC-256密码破解资源及运行时间估算

不可置否,这一结果可能会颠覆行业认知。此前RSA-2048分解需百万比特,如今万比特系统即可实现,并行架构更是将时间压缩至“实用级”。更重要的是,研究团队采用的低深度电路与并行操作,仍有进一步优化空间,未来运行时间可再降一个数量级。

量子计算竞争逻辑的转变

本研究通过创新性地结合高速率量子纠错码、中性原子平台和优化编译策略,将Shor算法的资源需求从百万级降低至万级量子比特,实现了量子计算向实用化迈进的关键一步。

这一突破的意义不仅在于具体数字的降低,更在于展示了通过跨层优化(从代码理论到硬件架构)实现量子资源高效利用的可行性。它为整个领域提供了新的技术路径和发展希望。

随着工程挑战的逐步解决,我们可能比预期更早地见证量子计算在解决实际问题中发挥重要作用。同时,这一进展也提醒我们,后量子密码的迁移不再是遥远的选择,而是紧迫的必要。量子计算的时代,正以超越我们想象的速度加速到来。

当然,这项研究的意义,也早已超越了单一论文或技术路线本身。

首先,它改变了量子计算的评价标准。过去,人们更关注“量子比特数量”或“量子优越性”;而现在,系统级能力、架构设计与纠错效率,正在成为新的核心指标。

其次,它重塑了技术路线的竞争格局。中性原子从此前的“潜力路线”,转变为最有可能实现大规模容错计算的候选之一,与超导、离子阱、光量子等主流技术路线形成新的竞争关系。

更重要的是,它重新定义了时间预期。如果按照当前技术进展速度,万比特级量子计算系统,可能已经进入未来5到10年的可实现区间。

总之,万比特级别的硬件需求,让量子计算机的研发成本、制备难度大幅降低,具备了商业化量产的基础。未来,中性原子量子计算机或许可广泛应用于密码分析、材料模拟、药物研发、优化求解等领域,量子算力将从实验室走向产业端,催生全新的量子计算产业生态。

参考链接

https://arxiv.org/abs/2603.28627

声明:本文来自光子盒,版权归作者所有。文章内容仅代表作者独立观点,不代表安全内参立场,转载目的在于传递更多信息。如有侵权,请联系 anquanneican@163.com。