最近在思考未来软件安全的发展趋势,正好把阶段性的思考形成文章与大家探讨。安智客试图从硬件安全、软件安全以及业务的诉求出发,梳理出未来软件安全的机会点。欢迎大家一块探讨。

安全从业者脑中有一系列的安全名词,比如安全三要素Confidenciality 、Integrity、Availability,比如硬件安全品牌TPM、TrustZone、SGX、Titan-M,比如软件层面的安全能力Isolation、Access Control,又比如漏洞缓解措施DEP、ASLR、CFI。从这些名词可以看出,软件最基础的安全能力都得自于硬件的支持,如果一个硬件没有特权级别,那就不要期望能实现什么安全能力了(没有MPU,基本的隔离都没办法做了)。硬件能力如同原材料,能做成什么样的美味佳肴就靠厨师(工程师)的本领了。因此在考虑未来产品安全的发展趋势时,硬件安全的未来演进是非常值得参考的。硬件安全系列主要讲述下ARM指令集的演进、Intel SGX解决方案以及苹果和Google硬件安全芯片的应用。本篇文章就从我们最熟悉的ARM开始讲起。

ARM在v7架构中就已经有了Security Extension,也就是TrustZone,其目的也很简单,在不增加硬件成本的情况下为设备提供一个可信执行环境。此种情况下CPU分为两个模式,Normal World和Secure World,两个世界有其各自独立的MMU,与之配套的TZASC(用于隔离内存)、TZPC(用于隔离外设)以及CCI总线构成了Cortex系列上的可信执行环境。软件所需要做的无非是配置好两个世界的切换,构建Secure World的OS和安全能力。在安全世界,软件开发者基于MMU构建了DEP和ASLR,配合安全世界的特权级别划分(SEL0和SEL1)实现用户态和内核态隔离,用户态应用之间的隔离。除此之外,CPU指令直接支持AES和HASH算法让加解密算法在ARM处理器上执行的更加高效。

当前手机上的主流芯片都是基于ARM v8架构,比如苹果A12,高通骁龙855,海思麒麟980。而且已经明确能从ARM官网看到v8.x的演进,比如8.1/2引入PAN和UAO,让内核态的程序在一定程度上不允许访问用户空间的资源;8.3引入Pointer Authentication,这是一项关键更新,当前苹果的A12芯片已经具备了此硬件特性,此特性在硬件上实现了CFI(Control Flow Integrity),保证执行流的正确,防止ROP的攻击。而在v8.4,ARM会在安全世界引入hypervisor,也就是SEL2,有了这一层,在软件层面就可以支持多个TEEOS,一定程度解决TEE碎片化问题,同时对于安全级别要求更高的业务(比如支付)可以跑在一个独立TEEOS中,与通用的TEEOS隔离开。v8.5 ARM会引入BTI(防JOP攻击)和Memory Tagging(内存区域标记,有效检测溢出和UAF漏洞)。

| 安全特性 | 英文拼写 | 说明 | 应对的攻击 | 体系架构 |

| XN | execute never | 不可执行。一般用于配置数据段不可执行,防止数据段注入可执行的shellcode。使用XN可执行DEP(Data execute Prevention,一般我们通常说的堆栈不可执行) | 任意地址读写、代码段覆盖 | v8以及以前 |

| PXN | Privileged Execute Never | 特权模式不可执行。防止在内核态模式下直接跳转到用户态的代码段进行提权攻击 | 执行流导向用户空间 | v8以及以前 |

| XOM | Execute Only Memory | 内存只可执行,不可读。防止执行逻辑泄露。 | 信息泄露 | v8.1/2 |

| WXN | Write Execute Never | 可写的内存不可执行。防止注入的shellcode可被执行 | 任意地址读写 | v8.1/2 |

| PAN | Privileged Access Never | 两者配合使用,实现内核态不允许访问用户态应用的数据的效果。防止高权限的内核偷应用的数据。 | 数据流导向用户空间 | v8.1/2 |

| UAO | User Access Only | |||

| PA | Pointer Authentication | 函数指针检查,cpu在执行函数跳转时检查函数指针是否正确(使用MAC算法),防止跳转指针被修改。 | ROP/JOP攻击 | v8.3 |

| BTI | Branch Target Identifiers | 对间接跳转的目标进行限制。与PA结合使用极大程度减少控制流攻击 | JOP攻击 | v8.5 |

| MT | Memory Tagging | 内存区域进行标记,对保护区域访问必须使用具有相同标记的指针。可检测溢出、UAF类漏洞 | 防溢出、UAF | v8.5 |

| ASLR | address space layout randomization | 内存地址随机化。基于MMU进行实现,对于应用来说,每次动态加载时,起始地址不同,增加攻击难度,增加对特定地址植入代码的难度 | 特定地址定位 | v8以及以前 |

| CFI | Control Flow Integrity | 控制流完整性。防止ROP攻击 | ROP/JOP攻击 | N |

除了Cortex A系列指令集的演进,ARM还将TrustZone带入到了Cortex M系列,在MCU上构建一个可信执行环境。此处的TEE具备MCU的低功耗和相比A系列CPU安全世界与非安全世界更快的切换速度。在Cortex M上引入TrustZone主要用于安全启动、固件安全、创建可信根,同时可控制安全外设,比如独立的安全存储、随机数产生器、安全始终。M系列上虽然引入了隔离的安全世界,但不会降低业务的实时性(相比没有TEE的MCU的确定性时延)。当前已经有厂商生产了支持TrustZone的M系列的芯片,比如MicroChip的SAM L10和L11(基于Cortex M23),详细参考安智客之前的一篇《支持轻量化TEE的ARM Cortex-M23/33 芯片厂商》。值得注意的是,除了Cortex M23和M33,ARM也提供了一个新d IP CortexM35P,此MCU除了具备TrustZone能力外(防软件攻击),还具备防物理攻击的能力(继承自SC300的安全特性),可应用在某些高安领域,如果成本可以接受的话,有可能是未来IoT新品的主力。

专为防硬件攻击设计的SECUCORE SC300,cpu核心为ARM v7-M,SC300集合了Cortex M3以及防硬件攻击的能力(防侧信道攻击和故障注入攻击),之前基于Cortex M3开发过程序的工程师可以非常容易的切换到SC300进行代码开发。骁龙845中的SPU就是基于SC300,具备智能卡级别的安全能力,可用于移动支付业务的部署。

除了CPU和MCU,ARM还提供很多安全IP,比如CryptoCell、CryptoIsland,前者提供硬件的加解密能力,后者除了提供加解密能力外还提供可编程的能力(内置了MCU)。

以上都是为ARM为Security而设计的IP,除此之外,ARM也在为Safety设计专门的IP,比如Cortex R52。

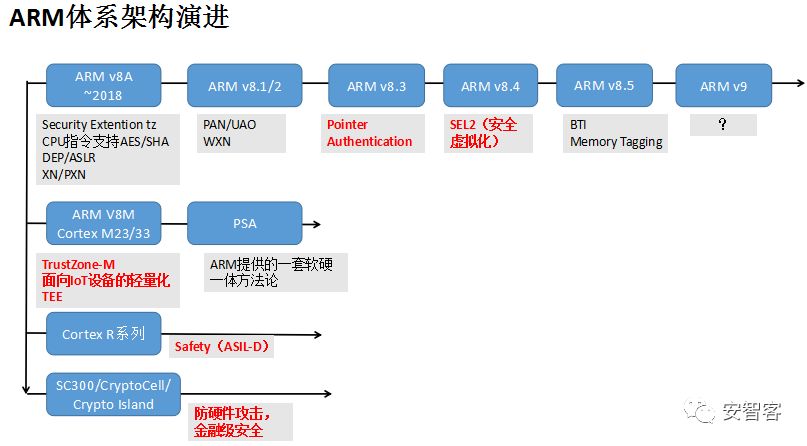

综合上面的描述,我们可以勾勒出如下ARM体系架构演进的路线。

由此可以看出,ARM不断通过硬件指令集的扩展从硬件层面直接防止控制流和数据流的攻击,提升黑客攻击难度;同时ARM将TrustZone引入IoT领域,支持轻量化TEE的部署,在IoT领域为安全业务提供可信执行环境和可信根。有了这些丰富的硬件安全能力,软件开发者就需要考虑如何使能这些安全能力,构建更安全可信的系统。

原材料已经准备好,就看厨子的水平了。

不能写公众号的工程师不是个好厨子。

参考文档:

- PA介绍:https://www.qualcomm.com/media/documents/files/whitepaper-pointer-authentication-on-armv8-3.pdf

- ARM V8.3介绍:https://community.arm.com/developer/ip-products/processors/b/processors-ip-blog/posts/armv8-a-architecture-2016-additions

- ARM V8.5介绍:https://community.arm.com/developer/ip-products/processors/b/processors-ip-blog/posts/arm-a-profile-architecture-2018-developments-armv85a

- TrustZone For Cortex M:https://www.arm.com/why-arm/technologies/trustzone-for-cortex-m

- 安智客:支持轻量化TEE的ARM Cortex-M23/33 芯片厂商

- Cortex M35P介绍:https://community.arm.com/developer/ip-products/processors/b/processors-ip-blog/posts/arm-cortex-m35p-multilayered-security-at-heart-of-your-device?_ga=2.234635739.438561052.1554817092-220590123.1554817092

声明:本文来自安智客,版权归作者所有。文章内容仅代表作者独立观点,不代表安全内参立场,转载目的在于传递更多信息。如有侵权,请联系 anquanneican@163.com。